SoiP1549 3500

# 日本国特許庁 JAPAN PATENT OFFICE

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office

出願年月日

Date of Application:

2000年10月10日

出願番号

Application Number:

特願2000-309506

出 願 人 Applicant(s):

ソニー株式会社

2001年 8月31日

特許庁長官 Commissioner, Japan Patent Office

【書類名】

特許願

【整理番号】

0000525503

【あて先】

特許庁長官殿

【国際特許分類】

H01L 23/29

H01L 23/31

H01L 21/60

【発明者】

【住所又は居所】

宮城県加美郡中新田町字雁原325番地ソニー中新田株

式会社内

【氏名】

吉沢 明

【特許出願人】

【識別番号】

000002185

【住所又は居所】

東京都品川区北品川6丁目7番35号

【氏名又は名称】

ソニー株式会社

【代表者】

出井 伸之

【代理人】

【識別番号】

100078145

【住所又は居所】

東京都新宿区西新宿7丁目18番18号 新宿税理士ビ

ル406号 松村内外特許事務所

【弁理士】

【氏名又は名称】

松村 修

【電話番号】

03-3361-2805

【手数料の表示】

【予納台帳番号】

014410

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【包括委任状番号】 9708409

【プルーフの要否】 要

## 【書類名】 明細書

【発明の名称】 半導体装置およびその製造方法

#### 【特許請求の範囲】

## 【請求項1】

所定の回路が設けられ、かつ外表面に電極が設けられた半導体チップと、 前記半導体チップがマウントされたインターポーザ基板と、

を有し、前記半導体素子と前記インターポーザ基板とが異方性導電層を介して 互いに接合されるとともに、前記半導体素子の電極と前記インターポーザ基板の 電極とが前記異方性導電層によって互いに接続されていることを特徴とする半導 体装置。

#### 【請求項2】

前記インターポーザ基板の前記半導体チップがマウントされた面とは反対側の 面に配線層を有する絶縁樹脂層が形成されていることを特徴とする請求項1に記 載の半導体装置。

#### 【請求項3】

配線層を有する絶縁樹脂層が複数層に積層して形成されていることを特徴とする請求項2に記載の半導体装置。

#### 【請求項4】

絶縁樹脂層が低弾性係数の物質から構成されることを特徴とする請求項2また は請求項3に記載の半導体装置。

#### 【請求項5】

最外層の絶縁樹脂層の外表面に外部接続用電極が形成されていることを特徴と する請求項2または請求項3に記載の半導体装置。

#### 【請求項6】

前記インターポーザ基板の厚さが 0.5 mm以下であることを特徴とする請求 項1に記載の半導体装置。

### 【請求項7】

前記絶縁樹脂層に設けられている配線層の配線が湾曲した形状を有することを 特徴とする請求項1に記載の半導体装置。

## 【請求項8】

所定の回路が設けられた半導体チップを異方性導電層を介してインターポーザ 基板上にマウントし、

前記半導体チップの電極を前記異方性導電層を介して前記インターポーザ基板 の電極と接続することを特徴とする半導体装置の製造方法。

## 【請求項9】

前記半導体チップの電極以外の部位と前記インターポーザ基板の電極以外の部位とが前記異方性導電膜によって互いに絶縁されることを特徴とする請求項8に記載の半導体装置の製造方法。

## 【請求項10】

所定の回路が設けられた半導体チップを異方性導電層を介してインターポーザ 基板上にマウントする工程と、

前記インターポーザ基板の前記半導体チップがマウントされた面とは反対側の 面に絶縁樹脂層を形成する工程と、

前記絶縁樹脂層の外表面上に導電層を形成する工程と、

前記導電層を選択的に除去して配線を形成する工程と、

を具備することを特徴とする半導体装置の製造方法。

## 【請求項11】

前記絶縁樹脂層を形成する工程と、前記導電層を形成する工程と、前記配線を 形成する工程とを複数回繰返すことによって、前記インターポーザ基板の前記半 導体チップがマウントされた面とは反対側の面に配線層を有する絶縁樹脂層を複 数層に積層して形成することを特徴とする請求項10に記載の半導体装置の製造 方法。

## 【請求項12】

最外層の絶縁樹脂層の外表面上に外部接続用電極を形成することを特徴とする 請求項10または請求項11に記載の半導体装置の製造方法。

#### 【請求項13】

最外層の絶縁樹脂層の外表面上の前記外部接続用電極を残してそれ以外の領域 にソルダーレジストを塗布することを特徴とする請求項12に記載の半導体装置

の製造方法。

## 【請求項14】

前記外部接続用電極上に半田ボールを形成することを特徴とする請求項12に 記載の半導体装置の製造方法。

## 【請求項15】

複数の半導体チップを集合状態のインターポーザ基板上にマウントし、配線層を有する単層または多層の絶縁樹脂層を形成した後にそれぞれの半導体チップに対応して個片に切断することを特徴とする請求項10に記載の半導体装置の製造方法。

## 【発明の詳細な説明】

[0001]

## 【発明の属する技術分野】

本発明は半導体装置およびその製造方法に係り、とくに半導体チップをインターポーザ基板上にマウントするようにした半導体装置およびその製造方法に関する。

[0002]

#### 【従来の技術】

半導体装置を構成する半導体パッケージを極限までに小型化軽量化したパッケージとして、チップサイズパッケージが用いられるようになっている。このようなチップサイズパッケージは、半導体素子(チップ)をこの半導体素子よりも一回り大きなインターポーザ基板上にマウントするものである。このようなチップサイズパッケージにおいて、半導体チップの電極はフリップチップ接続によってインターポーザ基板上の電極に接続される。そして半導体チップとインターポーザ基板との間の隙間に樹脂を封入して封止する。

[0003]

## 【発明が解決しようとする課題】

このような従来のチップサイズパッケージは、半導体チップとインターポーザ 基板との間に充填される接着剤によって強固な構造になるものの、応力を吸収し 難い構造になる。従ってこのようなチップサイズパッケージから成る半導体装置

をマザーボードにマウントすると、チップサイズパッケージとマザーボードとの間の熱膨張差によって、半導体装置とマザーボードとの接続を行なっている半田接続バンプ等が損傷する可能性があり、信頼性に問題を残すことになる。

## [0004]

また上記のようなチップサイズパッケージは、半導体チップの電極とインターポーザ基板の電極とをフリップチップ接続しているために、両者を正しく位置合わせしなければならず、これによって高精度の位置決めを必要とする。また半導体チップとインターポーザ基板との間に樹脂を封入すると、工程に時間を要し、これによって生産性が低下する問題がある。

## [0005]

本発明はこのような問題点に鑑みてなされたものであって、マザーボードにマウントした場合における応力の吸収が容易であって、しかも生産性に優れた半導体装置およびその製造方法を提供することを目的とする。

## [0006]

## 【課題を解決するための手段】

半導体装置に関する主要な発明は、所定の回路が設けられ、かつ外表面に電極が設けられた半導体チップと、

前記半導体チップがマウントされたインターポーザ基板と、

を有し、前記半導体素子と前記インターポーザ基板とが異方性導電層を介して 互いに接合されるとともに、前記半導体素子の電極と前記インターポーザ基板の 電極とが前記異方性導電層によって互いに接続されていることを特徴とする半導 体装置に関するものである。

#### [0007]

ここで前記インターポーザ基板の前記半導体チップがマウントされた面とは反対側の面に配線層を有する絶縁樹脂層が形成されていてよい。また配線層を有する絶縁樹脂層が複数層に積層して形成されてよい。このような絶縁樹脂層が低弾性係数の物質から構成されることが好ましい。また最外層の絶縁樹脂層の外表面に外部接続用電極が形成され、このような外部接続用電極を利用してマザーボード上にマウントされる。また前記インターポーザ基板の厚さが0.5mm以下、

より好ましくは0.3mm以下の薄い基板を用いることが好適である。また前記 絶縁樹脂層に設けられている配線層の配線が湾曲した形状を有し、これによって 熱膨張差に伴う引張り応力を変形によって吸収することが好ましい。

[0008]

製造方法に関する主要な発明は、所定の回路が設けられた半導体チップを異方 性導電層を介してインターポーザ基板上にマウントし、

前記半導体チップの電極を前記異方性導電層を介して前記インターポーザ基板の電極と接続することを特徴とする半導体装置の製造方法に関するものである。 ここで前記半導体チップの電極以外の部位と前記インターポーザ基板の電極以外の部位とが前記異方性導電膜によって互いに絶縁されることになる。

[0009]

製造方法に関する別の主要な発明は、所定の回路が設けられた半導体チップを 異方性導電層を介してインターポーザ基板上にマウントする工程と、

前記インターポーザ基板の前記半導体チップがマウントされた面とは反対側の 面に絶縁樹脂層を形成する工程と、

前記絶縁樹脂層の外表面上に導電層を形成する工程と、

前記導電層を選択的に除去して配線を形成する工程と、

を具備することを特徴とする半導体装置の製造方法に関するものである。

[0010]

ここで前記絶縁樹脂層を形成する工程と、前記導電層を形成する工程と、前記配線を形成する工程とを複数回繰返すことによって、前記インターポーザ基板の前記半導体チップがマウントされた面とは反対側の面に配線層を有する絶縁樹脂層を複数層に積層して形成するようにしてよい。また最外層の絶縁樹脂層の外表面上に外部接続用電極を形成することが好ましい。また最外層の絶縁樹脂層の外表面上の前記外部接続用電極を残してそれ以外の領域にソルダーレジストを塗布することが好ましい。また前記外部接続用電極上に半田ボールを形成することが可能である。また複数の半導体チップを集合状態のインターポーザ基板上にマウントし、配線層を有する単層または多層の絶縁樹脂層を形成した後にそれぞれの半導体チップに対応して個片に切断するようにしてよい。

## [0011]

本願に含まれる発明の好ましい態様は、薄いインターポーザ基板上に半導体チップをフリップチップ接続するとともにその信頼性の向上を図るものである。すなわち一般にチップサイズパッケージの製造において、インターポーザ基板上に半導体チップを接合するが、チップの構造上から多層基板が必要であったり、マウントされるマザーボードとのストレスの緩和を考慮してある程度厚い、例えば0.5 mm以上のインターポーザ基板が使われる傾向にある。これに対して本願の好ましい態様においては、インターポーザ基板として0.5 mm以下、より好ましくは0.3 mm以下の1層の薄い基板を用いるようにしており、接続を確実に行なうとともに、フリップチップ接合の信頼性を向上させるようにしている。

## [0012]

ここで半導体チップとインターポーザ基板との接続を、両者の間に介在される 異方性導電膜を用いるようにしている。異方性導電膜はマトリックス樹脂中に外 表面が導電層によって覆われた樹脂粒子を混入したものである。このような異方 性導電膜によって熱圧着を行なうと、膜厚方向には導電性を生ずるとともに面方 向には絶縁性を生ずるために、対向する電極間の部分を永久接着するとともに電 極間の導通を図り、電極パターン間の絶縁を同時に形成することが可能になる。

#### [0013]

半導体チップがマウントされたインターポーザ基板の上記半導体チップがマウントされた面とは反対側の面に基板ビルドアップ技術を利用して、絶縁樹脂層を形成し、ビア形成、銅メッキ、配線形成を行なうことによって配線層を作る。このときの絶縁樹脂としては、超低弾性係数のゴム状の樹脂を用いることが好ましい。絶縁樹脂層は適当な厚さを有し、必要に応じて2~3層に積上げる。これによって薄いインターポーザ基板上に接続された半導体チップとマザーボードとの熱膨張係数の差を吸収することが可能になる。そして上記絶縁樹脂層の上に形成される配線層の配線形状は、直線状の形状を避けて湾曲した形状とし、熱膨張差に伴う変形が引張り応力を発生しないようにすることが好ましい。

## [0014]

このような態様に係る半導体装置によれば、異方性導電膜を応用したフリップ

チップ接続によって半導体チップの電極とインターポーザ基板の電極とを接続することが可能になり、フリップチップ接続の安定化と信頼性の向上とを図ることが可能になる。とくにインターポーザ基板が薄くてしかも簡素化できるために、接合条件が安定し、信頼性が向上する。

#### [0015]

またこのような異方性導電膜によって半導体チップと接続されたインターポーザ基板上に配線層を有する絶縁樹脂層を形成するようにしているために、マザーボードに搭載後の熱ストレスに対して柔軟な構造になり、このために使用時における信頼性が向上する。また配線の引回しの自由度があるために、半導体チップのウエハサイズに限りなく近づけることが可能であって、これによって超小型のチップサイズパッケージを提供できるようになる。またこのような半導体装置は、マルチチップモジュール等のモジュール化への広い範囲に応用することができる。

#### [0016]

#### 【発明の実施の形態】

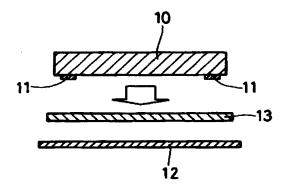

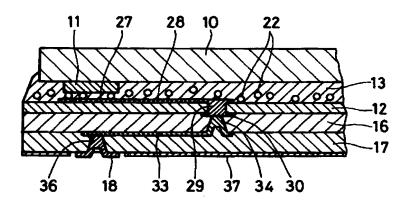

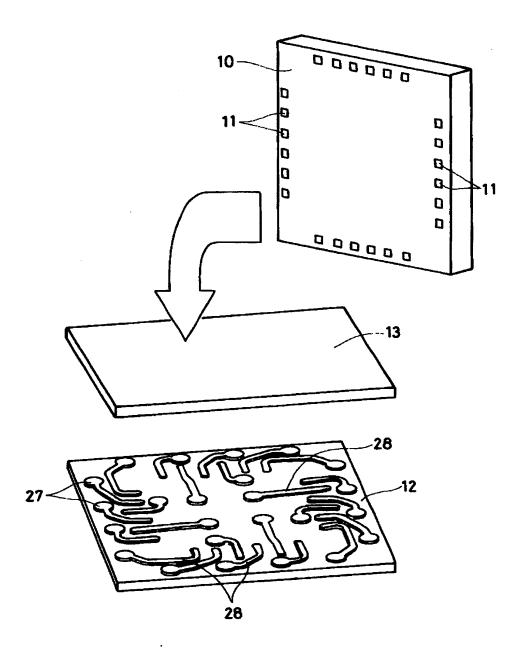

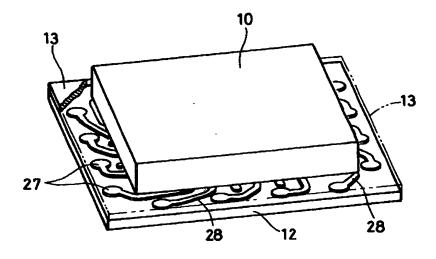

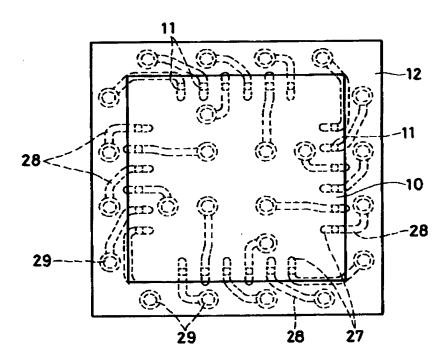

以下本発明を図示の一実施の形態によって説明する。図1は半導体チップ10とインターポーザ基板12との接合を示している。半導体10にはその接合面側に例えばアルミニウムパックから成る電極11が形成されている。そしてこのような半導体チップ10はインターポーザ基板12と異方性導電層13を介して接合される。

#### [0017]

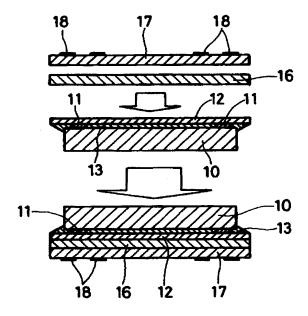

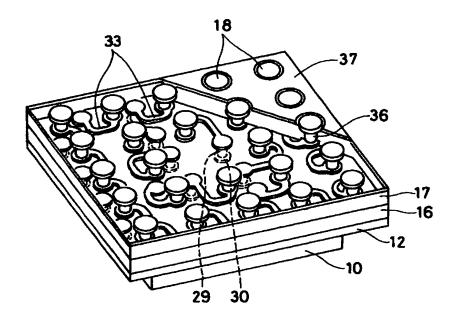

インターポーザ基板12と接合された後に、半導体チップ10上には図2に示すように絶縁樹脂層16、17がビルドアップされる。そして最外層の絶縁樹脂層17の外表面上には外部接続用電極18が形成される。このような外部接続用電極18がこの半導体装置の電極になり、マサーボードにこの半導体装置をマウントした場合に、外部接続用電極18によって導通が図られる。

#### [0018]

このように本実施の形態の半導体装置は、薄いインターポーザ基板12を用いるようにしており、このようなインターポーザ基板12上に半導体チップ10を

マウントしている。

[0019]

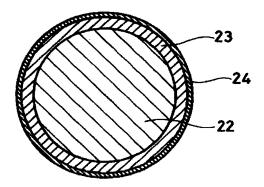

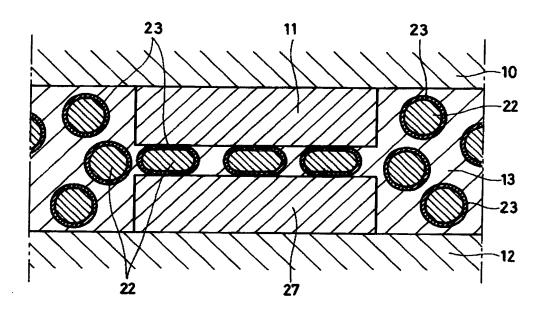

ここで半導体チップ10とインターポーザ基板12との接続は、図3~図5に示す異方性導電膜13によって行なわれる。異方性導電膜13は図3に示すようにエポキシ樹脂等のマトリックス樹脂から構成されるとともに、その中に樹脂粒子22を分散させたものである。ここでそれぞれの樹脂粒子22は図4に示すように球状をなすとともに、その外周部に金属メッキから成る金属層23が形成され、さらにその外周面を覆うように薄い絶縁被膜24が形成されている。

[0020]

このような異方性導電膜13を半導体チップ10とインターポーザ基板12との間に介在させて加熱および加圧を行なうと、図5に示すように半導体チップ10の電極11とインターポーザ基板の電極27との間においてこれらの電極11、27の高さによって樹脂粒子22が押潰され、外側の絶縁被膜24が破壊されて金属層23が露出する。これによって樹脂粒子22による半導体チップ10の電極11とインターポーザ基板12の電極27との電気的な接続が達成される。これに対して電極11、27が存在しない領域においては、半導体チップ10とインターポーザ基板12との間の隙間が大きいために樹脂粒子22は球状の形態をそのまま維持し、外周面の絶縁被膜24によって短絡が防止される。すなわち電極11、27以外の領域における導通が阻止され、これによって選択的な電気的接続が達成される。

[0021]

このように異方性導電膜13は、半導体チップ10とインターポーザ基板12との接合、両者の電極11、27の導通、および両者の電極11、27が形成されていない領域の絶縁の3つの機能を同時に達成することになる。すなわち異方性導電膜13を半導体チップ10とインターポーザ基板12とのによって挟着した状態で熱圧着を行なうと、異方性導電膜13の膜厚方向には導電性を有し、面方向には絶縁性を有する電気的異方性を発現することになる。これによって対向する電極11、27間の永久接着と、電極11、27間の導通と、電極11、27が形成されていない領域における半導体チップ10とインターポーザ基板12

との間の絶縁とが同時に達成される。

[0022]

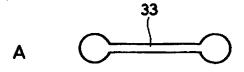

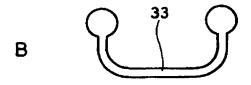

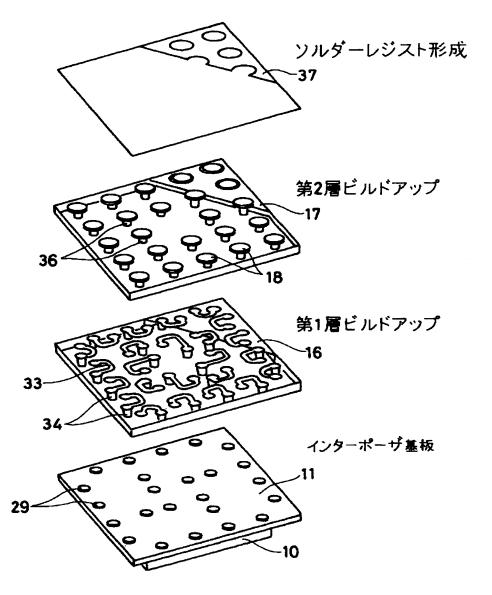

この後に図6~図8に示すように、この後にインターポーザ基板12の半導体チップ10がマウントされた面とは反対側の面に基板ビルドアップ技術を用いて絶縁樹脂層16、17を形成する。このときにビアの形成によって絶縁層16、17にそれぞれ層間接続手段34、36を形成し、絶縁層16の表面に形成された銅メッキをエッチングすることによって配線33を形成し、これによって信頼性の高いチップサイズパッケージを形成するようにしている。

[0023]

ここで絶縁樹脂層16に形成される配線33は図7Aに示すような直線状の形状を避け、図7Bに示すような湾曲した形状としている。このような湾曲した形状の配線33を形成するのは、応力を変形によって逃げ、これによって断線を防止することにある。

[0024]

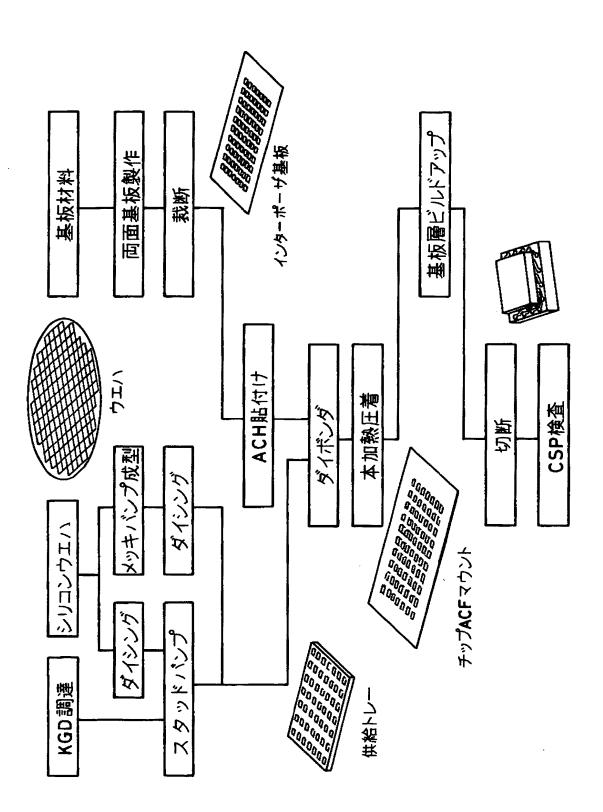

図9はこのような半導体装置の製造プロセスを示している。半導体チップはシリコンウエハから製作される。すなわちシリコンウエハをダイシングした後にスタッドバンプボンディングを行なうか、メッキバンプ成形した後にダイシングを行なって半導体チップを得る。なお良品のチップのみを選択して供給するKGD調達を利用してもよい。この場合にもスタッドバンプボンディングを行なう。

[0025]

これに対してインターポーザ基板は基板材料の片面または両面に配線を施して 片面基板または両面基板を集合状態で製造し、所定の大きさに裁断した状態で用 いる。

[0026]

この後に集合状態のインターポーザ基板12上に異方性導電膜13を介して半 導体チップ10をそれぞれのインターポーザ基板12に対応して貼付け、ダイボ ンダを行ない、加熱圧着することによって、半導体チップ10とインターポーザ 基板12との接合を集合状態で行なう。そしてこの後にインターポーザ基板12 の半導体チップ10がマウントされた面とは反対側の面にビルドアップによって

配線層33、18を有する絶縁樹脂層16、17を順次形成する。この後に集合 状態のインターポーザ基板12を切断し、それぞれの半導体チップ10に対応し た個片を切出すことによってチップサイズパッケージが得られる。このようなチップサイズパッケージは所定の検査工程に供される。

## [0027]

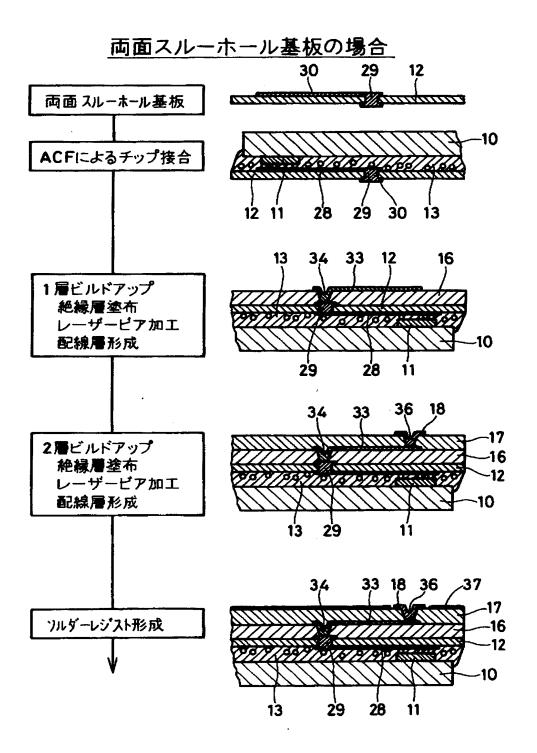

次にこの工程をより詳細に説明する。図10はインターポーザ基板12が両面スルーホール基板の場合の製造プロセスを示している。ここでインターポーザ基板12は0.3mm以下の薄い基板とし、極力単純形状のものを用いる。そして両面基板の場合には、インターポーザ基板12にスルーホール等の層間接続手段29によってランド30等の配線を両面に導く。

## [0028]

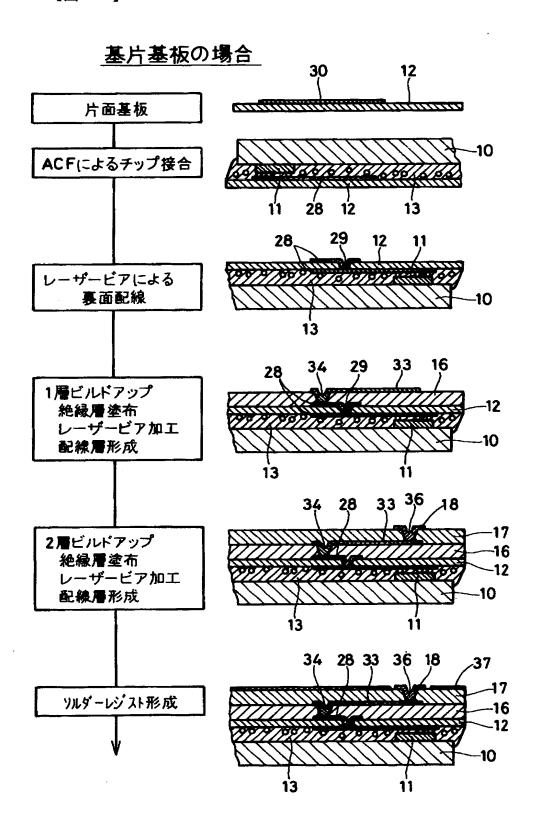

これに対してインターポーザ基板12が片面基板の場合には図11に示すように、異方性導電膜13によって半導体チップ10を接合した後に半導体チップ10のマウント面とは反対側の面からインターポーザ基板12に対してレーザ光等によってビアを形成し、銅メッキを施し、感光剤を塗布し、露光および現像を行ない、エッチング工程によってインターポーザ基板12の反対側の面に層間接続手段29と接続された配線28を形成する。

### [0029]

この後の絶縁樹脂層16、17を形成する工程は、図10に示す両面スルーホール基板から成るインターポーザ基板12を用いる場合と片面基板から成るインターポーザ基板12を用いる場合で差はない。この動作を説明すると、インターポーザ基板12の裏面であって半導体チップ10が搭載されていない面に絶縁樹脂を塗布して絶縁樹脂層16を形成する。絶縁樹脂としては硬化した時点でも弾性を有し、ゴム状の状態となる樹脂が選択される。またこのような絶縁樹脂層16の厚さは50μm以上とする。レーザによるビアの穿孔能力が高い場合には、さらに厚い絶縁樹脂層16を形成してよい。

### [0030]

レーザまたはフォトプロセスによって絶縁樹脂層16にビアを形成した後に、 このビアの内周面に銅メッキを施す。銅メッキは10~20μmとし、このよう

な銅メッキによって層間接続手段34を形成する。そしてこの後にフォトプロセスによって上記銅メッキをエッチングすることにより配線層33を形成する。配線33の引回しは上述の如く図7Aに示すような直線状の形状とせず、図7Bに示すような湾曲した形状とし、ストレスを逃げる構造にする。

## [0031]

この後にさらに絶縁樹脂を塗布して2層目の絶縁樹脂層17を形成する。このような絶縁樹脂層17にさらに上述の第1層の絶縁樹脂層16の場合と同様の方法で層間接続手段36を形成し、このような層間接続手段36と形成された外部接続用電極18を形成する。絶縁樹脂層の階層数は、2層以上とすることが好ましく、3層構造を採用することも可能である。層数の選択はバンプ密度との関係で行なえばよい。

## [0032]

この後最外層の絶縁樹脂層17の外表面であって半田接合部以外を覆うためにソルダーレジスト37を塗布してランドを形成する。ここでランド状の接続手段を用いるLGA(Land grid array)として使用する場合には、ランドを構成する外部接続用電極18に金フラッシュメッキを施すことが好ましい。また半球状の半田の突起を接続手段として用いるBGA(Ball grid array)とする場合には、ランドを構成する外部接続用電極18上に半田ボールを形成する。半田ボールはクリーム半田を印刷し、リフロー炉またはボールマウントリフロー炉によって半田を溶融して表面張力によって半球状の半田ボールを形成することにより行なう。

#### [0033]

図12〜図14は、このような製造工程における半導体チップ10とインターポーザ基板12との接続をより具体的に示したものであって、半導体チップ10 を異方性導電膜13を介してインターポーザ基板12に接続する状態を示している。

#### [0034]

これに対して図15~図17は、半導体チップ10がマウントされたインターポーザ基板12の上記半導体チップ10のマウント面とは反対側の面に絶縁樹脂

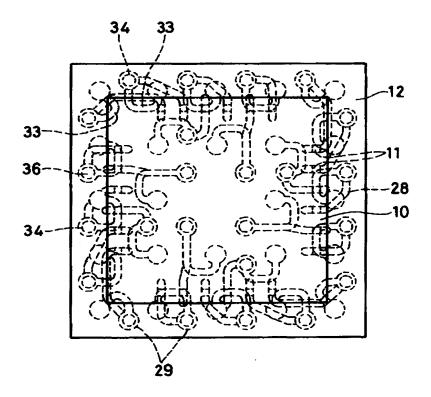

層16から成る第1ビルドアップ層と絶縁層17から成る第2ビルドアップ層と を順次形成する状態を示している。また図18は一実施の形態の半導体装置にお ける半導体チップ10、インターポーザ基板12、絶縁樹脂層16、および絶縁 樹脂層17のパターンの配置をそれぞれ示したものである。

[0035]

このように本実施の形態の半導体装置は、インターポーザ基板12上に形成されるビルドアップ層16、17の配線形成に当っては、2層以上とするとともに配線材の弾性や絶縁樹脂の柔軟性によって、応力歪みを逃がす構造を採用している。とくに絶縁樹脂層16、17に形成される配線33の引回しに当っては、とくに図7Aに示すような直線状の形状を避け、図7Bに示すようにループさせたり、湾曲した形状を採用する等の工夫を施し、これによって歪みに対応させ、応力緩和機能をもたせるようにしている。このときの電気的特性の問題に対応して、設計に当っては十分な配慮を行なうようにしている。また配線33を構成する銅箔の厚さと曲率とによって柔軟性をもたせた設計とするようにしている。

[0036]

このような半導体装置は各種の展開が可能である。すなわち共通のインターポーザ基板12上に複数の同一の種類または異なる種類の半導体チップ10を配したマルチチップモジュールへの展開が可能である。例えばインターポーザ基板12上にロジックICやメモリIC等の異種のICをマウントし、インターポーザ基板12上の配線層で結合して1つの機能をもたせたマルチチップモジュールパッケージとすることができる。このときにチップマウント側を樹脂で封止し、パッケージとしての体裁を整えることも可能である。

[0037]

またインターポーザ基板 1 2上に半導体チップ 1 0以外にチップコンデンサ等の小型部品を搭載し、1 つの機能をもたせたモジュールとし、これによってより高い機能をもたせた部品にすることが可能になる。

[0038]

【発明の効果】

本願の主要な発明は、所定の回路が設けられ、かつ外表面に電極が設けられた

半導体チップと、半導体チップがマウントされたインターポーザ基板と、を有し、半導体素子とインターポーザ基板とが異方性導電層を介して互いに接合されるとともに、半導体素子の電極とインターポーザ基板の電極とが異方性導電層によって互いに接続されるようにした半導体装置に関するものである。

[0039]

従ってこのような半導体装置によれば、異方性導電層を介して半導体素子とインターポーザ基板とが互いに接合されるとともに、両者の電極が互いに接続されることになる。従って半導体チップの電極とインターポーザ基板の電極との接続条件が安定し、信頼性が向上するようになる。

[0040]

製造方法に関する主要な発明は、所定の回路が設けられた半導体チップを異方 性導電層を介してインターポーザ基板上にマウントし、

前記半導体チップの電極を前記異方性導電層を介して前記インターポーザ基板 の電極と接続するようにしたものである。

[0041]

従って半導体チップとインターポーザ基板との接続が極めて容易にかつ安定的 に行なわれる半導体装置の製造方法を提供することが可能になる。

[0042]

製造方法に関する別の主要な発明は、所定の回路が設けられた半導体チップを 異方性導電層を介してインターポーザ基板上にマウントする工程と、インターポーザ基板の半導体チップがマウントされた面とは反対側の面に絶縁樹脂層を形成 する工程と、絶縁樹脂層の外表面上に導電層を形成する工程と、導電層を選択的 に除去して配線を形成する工程と、を具備するしたものである。

[0043]

従ってこのような半導体装置の製造方法によれば、インターポーザ基板の半導体チップがマウントされた面とは反対側の面に絶縁樹脂層をビルドアップした半 導体装置を安定的に製造することが可能になる。

【図面の簡単な説明】

【図1】

インターポーザ基板に対する半導体チップのマウントを示す縦断面図である。

## 【図2】

インターポーザ基板の半導体チップがマウントされた面とは反対側の面にビル ドアップ層を形成する動作を示す縦断面図である。

#### 【図3】

異方性導電膜の拡大断面図である。

## 【図4】

異方性導電膜中に分散された樹脂粒子の拡大縦断面図である。

#### 【図5】

異方性導電膜による電極間の接続を示す拡大縦断面図である。

#### 【図6】

完成した半導体装置の要部縦断面図である。

### 【図7】

絶縁樹脂層上に形成される配線の平面図である。

#### 【図8】

半導体装置の要部の外観斜視図である。

#### 【図9】

製造プロセスを示すブロック図である。

#### 【図10】

両面スルーホール基板から成るインターポーザ基板を用いたときの製造プロセスを示す縦断面図である。

#### 【図11】

片面基板から成るインターポーザ基板を用いたときの製造プロセスを示す縦断 面図である。

### 【図12】

半導体チップのインターポーザ基板に対する接続を示す外観斜視図である。

#### 【図13】

半導体チップがマウントされたインターポーザ基板の外観斜視図である。

## 【図14】

同平面図である。

#### 【図15】

半導体装置のビルドアップの状態を示す外観斜視図である。

### 【図16】

ビルドアップされた半導体装置の外観斜視図である。

## 【図17】

同半導体装置の要部平面図である。

#### 【図18】

半導体装置を構成する各層のパターンを示す平面図である。

### 【符号の説明】

10…半導体チップ、11…電極(パッド)、12…インターポーザ基板、13…異方性導電膜(層)、16、17…絶縁樹脂層、18…外部接続用電極、22…・樹脂粒子、23…金属層、24…絶縁被膜、27…電極、28…配線、29…層間接続手段、30…ランド、33…配線、34…層間接続手段、36…層間接続手段、37…ソルダーレジスト

【書類名】 図面【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

## 【書類名】 要約書

## 【要約】

### 【課題】

半導体チップとインターポーザ基板との接続が確実でしかも信頼性の高いチップサイズパッケージの半導体装置を提供することを目的とする。

## 【解決手段】

電極11を有する半導体チップ10とインターポーザ基板12との接続において、樹脂粒子22を分散させた異方性導電膜13を両者の間に介在させて加熱して接合を行なうようにしたものである。

### 【選択図】 図6

## 認定・付加情報

特許出願の番号

特願2000-309506

受付番号

50001308536

書類名

特許願

担当官

第五担当上席

0094

作成日

平成12年10月11日

<認定情報・付加情報>

【提出日】

平成12年10月10日

## 出願人履歴情報

識別番号

[000002185]

1. 変更年月日 1990年 8月30日

[変更理由] 新規登録

住 所 東京都品川区北品川6丁目7番35号

氏 名 ソニー株式会社